# LECTURE NOTES ON DIGITAL ELECTRIONICS AND MICROPROCESSOR

### Prepared By:

Prajnaparamita Kabi

lect E&TC Engg.

SYNERGY SCHOOL OF ENGINEERING

#### **BASICS OF DIGITAL ELECTRONICS**

The branch of electronics that deals with digital data in the form of codes. There are only two codes in digital electronics, and they are 0 and 1. 0 is considered to be low logic while 1 is considered to be high logic.

Digital Electronics can also be defined as the circuit which deals with Digital Signal is knows as Digital Electronics

#### **Advantages Of Digital Electronics**

- a. Digital Electronic circuits are relatively easy to design.

- b. It has higher precision rate in terms of accuracy.

- c. Transmitted signals are not lost over long distance.

- d. Digital Signals can be stored easily.

- e. Digital Electronics is more immune to 'error' and 'noise' than analog. But in case of high-speed designs, a small noise can induce error in the signal.

- f. The voltage at any point in a Digital Circuit can be either high or low; hence there is less chance of confusion.

- g. Digital Circuits have the flexibility that can change the functionality of digital circuits by making changes in software instead of changing actual circuit.

#### **Disadvantages of Digital Electronics**

- a. The real world is analog in nature, all quantities such as light, temperature, sound etc. Digital Systems is required to translate a continuous signal to discrete which leads to small quantization errors. To reduce quantization errors a large amount of data needs to be stored in Digital Circuit.

- b. Digital Circuits operate only with digital signals hence, encoders and decoders are required for the process. This increases the cost of equipment.

#### **Number System**

A digital system can understand positional number system only where there are a few symbols called digits and these symbols represent different values depending on the position they occupy in the number.

A value of each digit in a number can be determined using

- a. The digit

- b. The position of the digit in the number

- c. The base of the number system (where base is defined as the total number of digits available in the number system).

#### **Type number System**

- 1. Decimal Number System

- 2. Binary Number System

- 3. Octal Number System

- 4. Hexadecimal Number System

#### **Decimal Number System**

The number system that we use in our day-to-day life is the decimal number system. The decimal number system contains ten digits from 0 to 9.(0,1,2,3,4,5,6,7,8,&9). Base=10

The position in the decimal number system specifies the power of the base (10).

#### **Example**

Mathematically, we can write it as

$$2541 = (2 \times 1000) + (5 \times 100) + (4 \times 10) + (1 \times 1)$$

$$= (2 \times 10^{3}) + (5 \times 10^{2}) + (4 \times 10^{1}) + (1 \times 10^{0})$$

$$= 2541$$

#### **Binary Number System**

Generally, a binary number system is used in the digital computers. In this number system, it carries only two digits, either 0 or 1

The binary number system contains 2 digits from 0 &1

Base=10

The position in the binary number system specifies the power of the base (2)

Mathematically, we can write it as

$$1101.011 = (1 \times 2^3) + (1 \times 2^2) + (0 \times 2^1) + (1 \times 2^0) + (0 \times 2^{-1}) + (1 \times 2^{-2}) + (1 \times 2^{-3})$$

Octal Number System

The octal number system contains 8 digits from 0 to 7(i.e. 0,1,2,3,4,5,6&7) Base=8

The position in the octal number system specifies the power of the base (8)

Mathematically, we can write it as

$$12570 = (1 \times 8^4) + (2 \times 8^3) + (5 \times 8^2) + (7 \times 8^1) + (0 \times 8^0)$$

#### **Hexadecimal Number System**

Uses 10 digits and 6 letters, 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F.

Letters represents numbers starting from 10. A = 10, B = 11, C = 12, D = 13, E = 14, F = 15. Base = 16

The position in the Hexadecimal Number System number system specifies the power of the base (8)

Mathematically, we can write it as

$$19FDE_{16} = (1 \times 16^4) + (9 \times 16^3) + (F \times 16^2) + (D \times 16^1) + (E \times 16^0)$$

#### **Number System and Base Conversions**

Electronic and Digital systems may use a variety of different number systems, (e.g. Decimal, Hexadecimal, Octal, Binary).

A number N in base or radix b can be written as:

$$(N)b = dn-1 dn-2 --- -- d1 d0 . d-1 d-2 --- -- d-m$$

In the above, dn-1 to d0 is the integer part, then follows a radix point, and then d-1 to d-m is the fractional part.

dn-1 = Most significant bit (MSB)

d-m = Least significant bit (LSB)

| Base | Representation |  |

|------|----------------|--|

| 2    | Binary         |  |

| 8    | Octal          |  |

| 10   | Decimal        |  |

| 16   | Hexadecimal    |  |

### 1. Decimal to Binary

Convert (34.25)<sub>10</sub> to Binary equivalent

**Step 1:** Divide the number 34 and its successive quotients with base 2.

Step 2:

Now, perform the multiplication of 0.25 and successive fraction with base 2.

| Operation | Result | carry |

|-----------|--------|-------|

| 0.25×2    | 0.50   | 0     |

| 0.50×2    | 0      | 1     |

$$(0.25)_{10} = (.01)_2$$

Final Result is

$$(34.25)_{10} = (100010.01)_2$$

### 2. Binary to Decimal

Convert (1010.01)2 to equivalent Decimal No.

$$(1010.01)_2 = 1x2^3 + 0x2^2 + 1x2^1 + 0x2^0 + 0x2^{-1} + 1x2^{-2} = 8 + 0 + 2 + 0 + 0 + 0.25 = 10.25$$

=  $(10.25)_{10}$

#### 3. Decimal to Octal

Convert (86)<sub>10</sub> to Octal equivalent

**Step 1:** Divide the number 34 and its successive quotients with base 8.

| 8 <u>)86</u> | Remainder |  |

|--------------|-----------|--|

| 8)10         | 6 ♠       |  |

| 8) 1         | 2         |  |

| 0            | 1         |  |

#### Step 2:

Now perform the multiplication of 0.35 and successive fraction with base 8.

| <b>Operation</b> | Result | carry |

|------------------|--------|-------|

| 0.35X8           | 2.8    | 2     |

| 0.8X8            | 6.4    | 6     |

| 0.4X8            | 3.2    | 3     |

| 0.3X8            | 2.4    | 2     |

$$(0.35)_{10} = (2632)_8$$

So, the octal number of the decimal number 86.35 is 126.2632

#### 4. Octal to Decimal

$$(12.2)_8$$

1 x 8<sup>1</sup> + 2 x 8<sup>0</sup> +2 x 8<sup>-1</sup> = 8+2+0.25 = 10.25

$(12.2)_8 = (10.25)_{10}$

### 5. Hexadecimal to Binary

To convert from Hexadecimal to Binary, write the 4-bit binary equivalent of hexadecimal.

| Binary equivalent | Hexadecimal |

|-------------------|-------------|

| 0000              | 0           |

| 0001              | 1           |

| 0010              | 2           |

| 0011              | 3           |

| 0100              | 4           |

| 0101              | 5           |

| 0110              | 6           |

| 0111              | 7           |

| 1000              | 8           |

| 1001              | 9           |

| 1010              | Α           |

| 1011              | В           |

| 1100              | С           |

| 1101              | D           |

| 1110              | E           |

| 1111              | F           |

### **Example**

$(3A)_{16} = (00111010)_2$

### 6. Binary to Hexadecimal

To convert from Binary to Hexadecimal, start grouping the bits in groups of 4 from the right-end and write the equivalent hexadecimal for the 4-bit binary. Add extra 0's on the left to adjust the groups.

1111011011 <u>0011 1101 1011</u> (001111011011)<sub>2</sub> = (3DB)<sub>16</sub>

#### 7. Hexa-decimal to Decimal Conversion

The process of converting hexadecimal to decimal is the same as binary to decimal. The process starts from multiplying the digits of hexadecimal numbers with its corresponding positional weights. And lastly, we add all those products.

Example 1: (152A.25)<sub>16</sub>

(152A.25)<sub>16</sub>=

$$(1\times16^3)+(5\times16^2)+(2\times16^1)+(A\times16^0)+(2\times16^{-1})+(5\times16^{-2})$$

=5418.14453125

#### 8. Decimal to Hexadecimal

2861<sub>10</sub>=B2D<sub>16</sub>

#### Binary addition, subtraction, Multiplication and Division

#### 1.Binary addition

| Case | А | + | В | Sum | Carry |

|------|---|---|---|-----|-------|

| 1    | 0 | + | 0 | 0   | 0     |

| 2    | 0 | + | 1 | 1   | 0     |

| 3    | 1 | + | 0 | 1   | 0     |

| 4    | 1 | + | 1 | 0   | 1     |

In fourth case, a binary addition is creating a sum of (1 + 1 = 10) i.e. 0 is written in the given column and a carry of 1 over to the next column.

### **Example - Addition**

#### 2. Binary Subtraction

**Subtraction and Borrow**, these two words will be used very frequently for the binary subtraction. There are four rules of binary subtraction.

| Case | Α | 18  | В | Subtract | Borrow |

|------|---|-----|---|----------|--------|

| 1    | 0 | :7: | 0 | 0        | 0      |

| 2    | 1 | -   | 0 | 1        | 0      |

| 3    | 1 |     | 1 | 0        | 0      |

| 4    | 0 |     | 1 | 0        | 1      |

7

#### Example - Subtraction

#### 3. Binary Multiplication

Binary multiplication is similar to decimal multiplication. It is simpler than decimal multiplication because only 0s and 1s are involved. There are four rules of binary multiplication.

| Case | Α | х | В | Multiplication |

|------|---|---|---|----------------|

| 1    | 0 | х | 0 | 0              |

| 2    | 0 | х | 1 | 0              |

| 3    | 1 | х | 0 | 0              |

| 4    | 1 | X | 1 | 1              |

### Example - Multiplication

Example:

0011010 x 001100 = 100111000

.1's complement and 2's complement numbers for a binary number

### a.1's complement

### 1's complement

**1's complement** of a binary number is another binary number obtained by toggling all bits in it, i.e., transforming the 0 bit to 1 and the 1 bit to 0.

Original value 1's complement

$$0 \longrightarrow 1$$

$0 \longrightarrow 1$

Examples:

1's complement of 7 (0111) is 8 (1000)

1's complement of 12 (1100) is 3 (0011)

#### **Use of 1's complement**

The main use of 1's complement is to represent a signed binary number. Apart from this, it is also used to perform various arithmetic operations such as addition and subtraction.

In signed binary number representation, we can represent both positive and negative numbers

#### .2's complement

**2's complement** of a binary number is 1 added to the 1's complement of the binary number.

| i.e. | Original value | 1's complement | 2's complement |

|------|----------------|----------------|----------------|

|      | 1011           | 0100           | 0100+1=0101    |

|      | 1101           | 0010           | 0010+1=0011    |

#### **Use of 2's complement**

Negative binary numbers are represented in 2's complement form so that the same logic circuit can be used to perform addition as well as subtraction

Subtraction of binary numbers in 2's complement method.

#### The operation is carried out by means of the following steps:

- (i) Find the 2's complement of the subtrahend(negative no. only, because 2's complement of positive no. is remain same) of given no..

- (ii) Then it is added to the minuend.(add 2's complemented with positive given no.)

- (iii)If the final carry over of the sum is 1, it is dropped and the result is positive.

- (iv) If there is no carry over, the two's complement of the sum will be the result and it is negative.

### **Examples:**

(i) 110110 - 10110

#### **Solution:**

Now, 2's complement of 010110 is (101101 + 1) i.e.101010. Adding this with the minuend.

1 1 0 1 1 0 Minuend

#### 1 0 1 0 1 0 2's complement of subtrahend

Carry over  $1 \quad 1 \quad 0 \ 0 \ 0 \ 0$  Result of addition After dropping the carry over we get the result of subtraction to be 100000.

#### (ii) 10110 - 11010

#### **Solution:**

2's complement of 11010 is (00101 + 1) i.e. 00110. Hence

Minued - 10110

2's complement of subtrahend - 00110

Result of addition - 11100

As there is no carry over, the result of subtraction is negative and is obtained by writing the 2's complement of 11100 i.e.(00011 + 1) or 00100.

Hence the difference is – 100.

Use of weighted and Un-weighted codes & write Binary equivalent number for a number in 8421, Excess-3 and Gray Code and vice-versa.

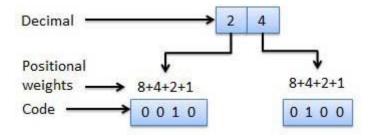

### Weighted code

Weighted binary codes are those binary codes which obey the positional weight principle. Each position of the number represents a specific weight. Several systems of the codes are used to express the decimal digits 0 through 9. In these codes each decimal digit is represented by a group of four bits.

- a. BCD (8421)

- b. 6311

- c. 2421

- d. 642-3

- **e.** 84-2-1

### **Use of Weighted codes**

- a) Data manipulation during arithmetic operation.

- b) Weighted binary code is essential for displaying numeric values in digital devices such as voltmeters and calculators

- .c) To represent the decimal digits in calculators, volt meters etc.

#### **Non-Weighted Codes**

In this type of binary codes, the positional weights are not assigned. The examples of non-weighted codes are Excess-3 code and Gray code.

### Non weighted codes are used in:

- a) To perform certain arithmetic operations.

- b) Shift position encodes.

- c) Used for error detecting purpose.

#### **Excess-3 code**

The Excess-3 code is also called as XS-3 code. It is non-weighted code used to express decimal numbers. The Excess-3 code words are derived from the 8421 BCD code words adding (0011)<sub>2</sub> or (3)10 to each code word in 8421. The excess-3 codes are obtained as follows –

### Example

| Decimal | BCD     | Excess-3   |

|---------|---------|------------|

|         | 8 4 2 1 | BCD + 0011 |

| 0       | 0 0 0 0 | 0 0 1 1    |

| 1       | 0 0 0 1 | 0 1 0 0    |

| 2<br>3  | 0 0 1 0 | 0 1 0 1    |

| 3       | 0 0 1 1 | 0 1 1 0    |

| 4       | 0 1 0 0 | 0 1 1 1    |

| 5       | 0 1 0 1 | 1 0 0 0    |

| 6       | 0 1 1 0 | 1 0 0 1    |

| 7       | 0 1 1 1 | 1 0 1 0    |

| 8       | 1 0 0 0 | 1 0 1 1    |

| 9       | 1 0 0 1 | 1 1 0 0    |

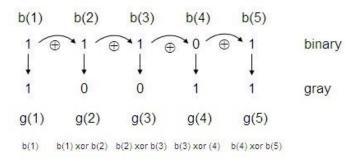

### **Gray Code**

It is the non-weighted code and it is not arithmetic codes. That means there are no specific weights assigned to the bit position. It has a very special feature that, only one

bit will change each time the decimal number is incremented as shown in fig. As only one bit changes at a time, the gray code is called as a unit distance code. The gray code is a cyclic code. Gray code cannot be used for arithmetic operation.

### **Convert a binary number to a Gray number**

Let's understand the algorithm to go from binary to Gray. See the conversion from `11101' binary to its equivalent in Gray code.

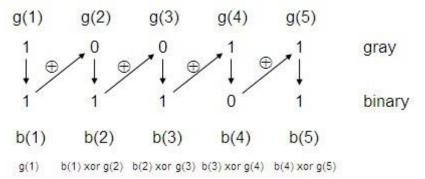

### Convert a Gray number to a binary number

Let's understand the algorithm to go from binary to Gray. See the conversion from '11101' binary to its equivalent in Gray code.

### **Application of Gray code**

- Gray code is popularly used in the shaft position encoders.

- A shaft position encoder produces a code word which represents the angular position of the shaft.

### Importance of parity Bit.

A parity bit is an extra bit included in binary message to make total number of 1's either odd or even. Parity word denotes number of 1's in a binary string. There are two parity system-even and odd.

### Even parity system

In even parity system 1 is appended to binary string it there is an odd number of 1's in string otherwise 0 is appended to make tot 1 even number of 1's.

### Odd parity system

In odd parity system, 1 is appended to binary string if there is even a number of 1's to make an odd number of 1's

### Importance of parity Bit.

The purpose of a parity bit is to provide a simple way to check for Errors

## Logic Gates: AND, OR, NOT, NAND, NOR and EX-OR gates with truth table.

### What is Logic Gates?

Logic gates are the basic building blocks of any digital system. It is an electronic circuit having one or more than one input and only one output. The relationship between the input and the output is based on a certain logic. Based on this, logic gates are named as AND gate, OR gate, NOT gate etc.

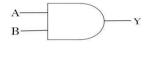

#### **AND Gate**

An AND gate is a logic gate having two or more inputs and  $\varepsilon$  single output. An AND gate operates on logical multiplication rules

Expression for AND gate Y=A.B

Truth Table of AND gate

| In | Input |   |

|----|-------|---|

| Α  | В     | Y |

| 0  | 0     | 0 |

| 0  | 1     | 0 |

| 1  | 0     | 0 |

| 1  | 1     | 1 |

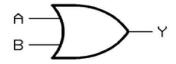

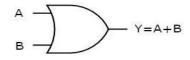

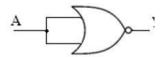

### **OR Gate**

Expression for OR gate Y=A+B

### **Truth Table**

| In | Input |   |

|----|-------|---|

| Α  | В     | Υ |

| 0  | 0     | 0 |

| 0  | 1     | 1 |

| 1  | 0     | 1 |

| 1  | 1     | 1 |

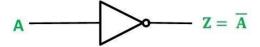

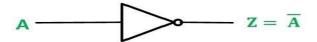

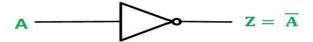

### **NOT Gate**

The NOT gate is the most basic logic gate of all other logic gates. NOT gate is also known as an **inverter**

NOT gate only has one input and one output it converts 0 into 1 or 1 into 0.

Expression for NOT gate  $Z=\overline{A}$

### **Truth Table**

| Inputs | Outputs |  |

|--------|---------|--|

| Α      | Υ       |  |

| 0      | 1       |  |

| 1      | 0       |  |

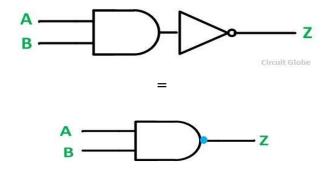

#### **NAND** Gate

The NAND gate is a special type of logic gate in the digital logic circuit.

The NAND gate is the combination of AND -NOT gate

The NAND gate is the universal gate. It means all the basic gates such as AND, OR, and NOT gate can be constructed using a NAND gate. The output state of the NAND gate will be low only when all the inputs are high. Simply, this gate returns the complement result of the AND gate.

Expression for NAND gate  $Z=\overline{A.B}$

### **Truth Table**

| Input |   | Out Put            |  |

|-------|---|--------------------|--|

| A     | В | $Z=\overline{A.B}$ |  |

| 0     | 0 | 0                  |  |

| 0     | 1 | 1                  |  |

| 1     | 0 | 1                  |  |

| 1     | 1 | 0                  |  |

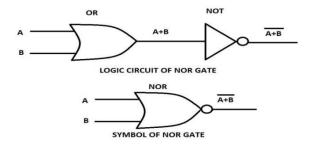

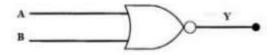

#### **NOR Gate**

The NOR gate is also a universal gate

The NOR gate is the combination of the OR -NOT gate

The NOR gate is the universal gate. It means all the basic gates such as AND, OR, and NOT gate can be constructed using a NOR gate.

The output state of the NOR gate will be high only when all of the inputs are low. Simply, this gate returns the complement result of the OR gate

Expression for Nor gate  $Z=\overline{A+B}$

### **Truth Table**

| Input |   | Out Put            |  |

|-------|---|--------------------|--|

| A     | В | $Z=\overline{A+B}$ |  |

| 0     | 0 | 1                  |  |

| 0     | 1 | 0                  |  |

| 1     | 0 | 0                  |  |

| 1     | 1 | 0                  |  |

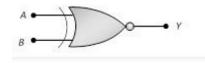

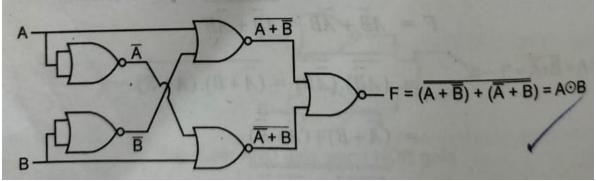

#### **EX-OR**

Expression for EX-OR gate  $Z=(\overline{A} B+A\overline{B})$

### **Truth Table**

| Input |   | Out Put       |  |

|-------|---|---------------|--|

| A     | В | <b>Z=A</b> ⊕B |  |

| 0     | 0 | 1             |  |

| 0     | 1 | 0             |  |

| 1     | 0 | 0             |  |

| 1     | 1 | 0             |  |

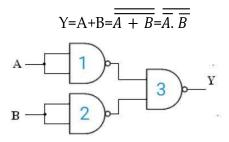

Realize AND, OR, NOT operations using NAND, NOR gates.

NAND and NOR gates provide the following merits in the digital logic system design

- 1. Fabrication of NAND and NOR gates are easier than basic gates using in the integrated digital logic families

- 2. Number of transistors used to design NAND and NOR gates are also less than AND and OR gates. Since the core area reduces in the integrated digital circuits.

- 3. The conversion of NAND and NOR are more conveniet in digital design.

- 4. All other logic gates can be realized completely using NAND or NOR gates.

- 5. Any digital ckt. can be implemented perfectly using either NAND or NOR gates thus these are called as universal gate

#### Implementation of Logic gates using NAND Gate

### i) NOT gate

The logic symbol and Boolean expression of NOT gate is represented by

NAND equivalent representation for NOT gate is

$$F = \overline{A} = \overline{A} \cdot \overline{A}$$

The above expression indicates that if the input terminals of NAND gate are Same shown in fig

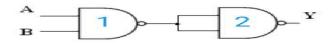

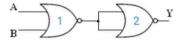

### ii) AND Gate

The logic symbol and Boolean expression of AND gate is represented by

Y=A.B

NAND equivalent representation for AND gate is

$$Y=A.B=\overline{A.B}$$

### Now above expression can drawn as

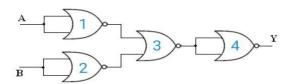

### iii) OR gate:

NAND equivalent representation for OR gate is

### iv) NOR gate:

$$Y=\overline{A+B}$$

NAND equivalent representation for NOR gate is

$$Y=\overline{A+B}=\overline{A+B}$$

$$=\overline{A}$$

$$=\overline{A}$$

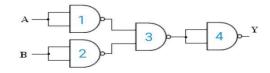

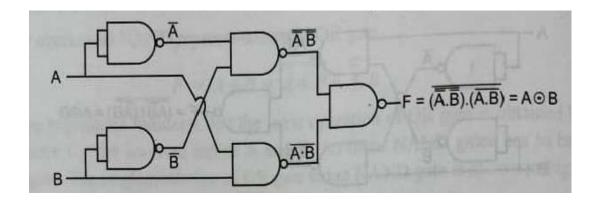

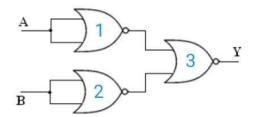

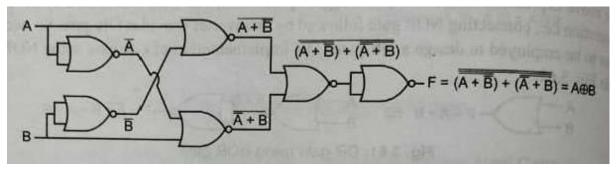

### v) Ex-OR gate:

$$Y = A \overline{B} + \overline{A} B$$

NAND equivalent representation for Ex-OR gate is

$$Y=A\overline{B}+\overline{A}B=\overline{A}\overline{B}+\overline{A}B$$

$$=(A\overline{B}).\overline{(AB)}$$

Now above expression can drawn as

### vi) Ex-NOR gate:

$Y=A \odot B=\overline{A} \overline{B} + AB$

NAND equivalent representation for Ex-NOR gate is

$$Y = \overline{A} \overline{B} + AB = \overline{A} \overline{B} + AB$$

$$= \overline{(\overline{A} \overline{B})} \cdot \overline{(\overline{AB})}$$

### • Implementation of Logic gates using NOR Gate

### i) NOT gate

The logic symbol and Boolean expression of NOT gate is represented by

NOR equivalent representation for NOT gate is

$$= \overline{A} + \overline{A}$$

Now above expression can drawn as

### ii) AND Gate

The logic symbol and Boolean expression of AND gate is represented by

NAND equivalent representation for AND gate is

$$Y=A.B=\overline{\overline{A.B}}$$

$$=\overline{\overline{A.+B}}$$

#### iii) OR gate:

The logic symbol and Boolean expression of OR gate is represented by

NOR equivalent representation for OR gate is

$$Y=A+B=\overline{A+B}$$

Now above expression can drawn as

### iv) NAND gate:

The logic symbol and Boolean expression of NAND gate is represented by

$$Y = \overline{A \cdot B}$$

NOR equivalent representation for NAND gate is

$$Y = \overline{A \cdot B} = \overline{A} + \overline{B} =$$

$$= \overline{A \cdot A} = \overline{A} + \overline{B} =$$

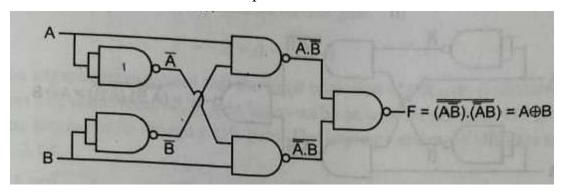

### v) Ex-OR gate:

The logic symbol and Boolean expression of Ex-OR gate is represented by

$$Y = A\overline{B} + \overline{A}B$$

NOR equivalent representation for Ex-OR gate is

$$Y = \overline{AB} + \overline{AB}$$

$$= (\overline{AB}). \overline{(\overline{AB})}$$

$$= (\overline{\overline{A} + B}). (\overline{A} + \overline{B})$$

$$= (\overline{\overline{A} + B}) + (\overline{\overline{A} + B})$$

$$= (\overline{\overline{A} + B}) + (\overline{\overline{A} + B})$$

$$= (\overline{\overline{A} + B}) + (\overline{\overline{A} + B})$$

Now above expression can drawn as

### i) Ex-NOR gate:

The logic symbol and Boolean expression of Ex-NOR gate is represented by

$Y=A \odot B=\overline{A} \overline{B} + AB$

NOR equivalent representation for Ex-NOR gate is

$$Y=A \odot B = \overline{\overline{A}} \overline{B} + \overline{A}B$$

$$= \overline{A}\overline{B} + \overline{\overline{A}B}$$

$$= (\overline{A}\overline{B}) \cdot (\overline{\overline{A}}B)$$

$$= (\overline{A} + B) \cdot (A + \overline{B})$$

$$= (\overline{A} + B) \cdot (A + \overline{B})$$

$$= (\overline{A} + B) + (\overline{A} + \overline{B})$$

Now above expression can drawn as

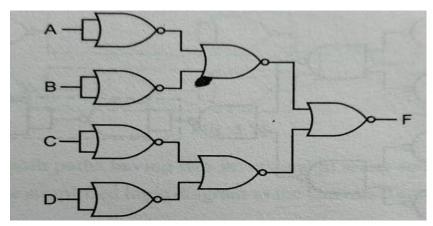

#### PROCEDURE TO IMPLEMENT THE BOOLEAN FUNCTION USING UNIVERSAL GATE:

- 1. Draw a logic diagram for the Boolean f unction using basic gates i.e. AND,OR,and NOT

- 2. Replace the gate with equivalent NAND or NOR realization.

- 3. If any path has continuous two inversions, discard those terms to reduce the number of logic gates employed to implement the Boolean function.

- 4. Redraw the simplified logic diagram as the Universal gates implementation of Boolean function.

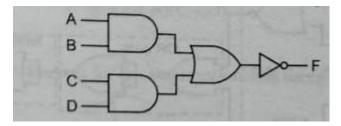

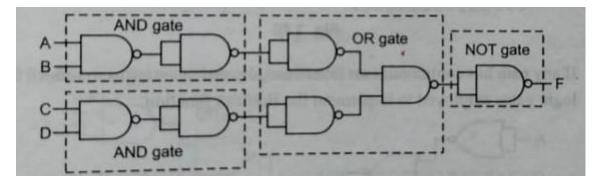

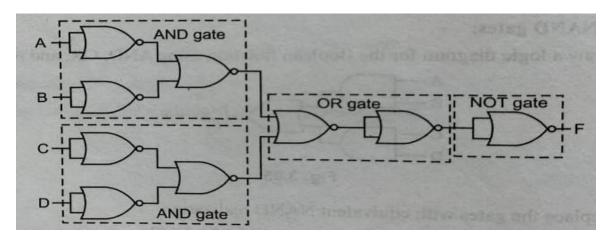

Example: Implement the following Boolean function using minimum number of (i)NAND gates, (ii)NOR gates

$$F = \overline{AB + CD}$$

Solution:

Given Boolean function,

$$F = \overline{AB + CD}$$

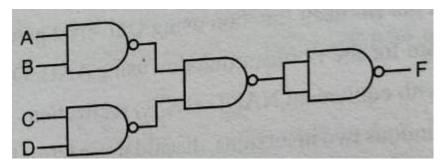

- (i) Using NAND gates:

- 1. Step:1 Draw a logic diagram for the Boolean f unction using basic gates i.e. AND,OR,and NOT

2. Step:2 Replace the gate with equivalent NAND realization.

3. Step:3 If any path has continuous two inversions, discard those terms to reduce the number of logic gates employed to implement the Boolean function.

In this case, both path are having two inversions in series so discard those inverter

4. Step:4Redraw the simplified logic diagram as the Universal gates implementation of Boolean function

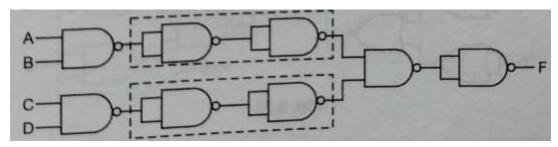

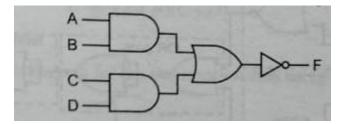

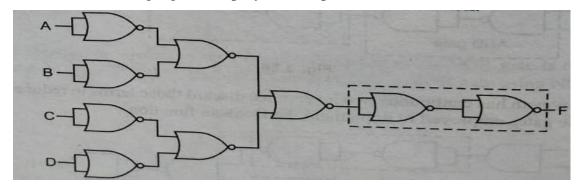

- (ii) Using NOR gates:

- 1. Step:1 Draw a logic diagram for the Boolean f unction using basic gates i.e. AND,OR,and NOT

2. Step:2 Replace the gate with equivalent NOR realization.

3. Step:3 If any path has continuous two inversions, discard those terms to reduce the number of logic gates employed to implement the Boolean function.

In this case, output section e having two inversions in series so discard those inverter

4. Step:4Redraw the simplified logic diagram as the Universal gates implementation of Boolean function

Different postulates and De-Morgan's theorems in Boolean algebra.

a.  $\overline{AB} = \overline{A} + \overline{B}$

b.

$$(\overline{A+B})=\overline{A}.\overline{B}$$

### Use Of Boolean Algebra For Simplification Of Logic Expression

### What is Boolean Algebra?

Boolean Algebra is used to analyze and simplify the digital (logic) circuits. It uses only the binary numbers i.e. 0 and 1. It is also called as **Binary Algebra** or **logical Algebra**. Boolean algebra was invented by **George Boole** in 1854

### Rule in Boolean Algebra

Following are the important rules used in Boolean algebra.

- I. Variable used can have only two values. Binary 1 for HIGH and Binary 0 for LOW.

- II. Complement of a variable is represented by an overbar (-). Thus, complement of variable B is represented as  $\overline{B}$ . Thus if B = 0 then  $\overline{B}$  = 1 and B = 1 then  $\overline{B}$  = 0.

- III. ORing of the variables is represented by a plus (+) sign between them. For example ORing of A, B, C is represented as A + B + C.

- IV. Logical ANDing of the two or more variable is represented by writing a dot between them such as A.B.C. Sometime the dot may be omitted like ABC.

#### BASIC LAWS OF BOOLEAN ALGEBRA:

#### 1. NOT Law:

i.

$$\overline{0}=1$$

ii.

$$\overline{1} = 0$$

iii.

$$A=\overline{\overline{A}}$$

#### 2. AND Laws

i.

$$A.0=0$$

ii. A.

$$1 = A$$

iii.

$$A. A = A$$

iv. A.

$$\overline{A} = 0$$

#### 3. OR Laws:

i.

$$A + 0 = A$$

ii.

$$A + 1 = 1$$

iii.

$$A + A = A$$

iv.

$$A + \overline{A} = 1$$

#### 4. Commutative Laws:

i.

$$A + A = B + A$$

ii.

$$A \cdot B = B \cdot A$$

iii.

$$A + B + C = C + B + C$$

iv.

$$A . B . C = B . C . A = C . A . B$$

5. Associative laws:

i.

$$A + (B + C) = (A + B) + C$$

ii.

$$A \cdot (B \cdot C) = (A \cdot B) \cdot C$$

6. Distributive law:

i.

$$A + B C = (A + B) (A + C)$$

ii.

$$A (B + C) = A B + A C$$

#### **BOOLEAN THEOREM**

#### 1. A + AB = A

Proof:

$$A+AB = A (B + \overline{B}) + AB$$

$=AB + A \overline{B} + AB$

$=AB + A\overline{B}$

$=A(B + \overline{B})$

$=A .1$

$=A$

2.

$$A(A + B) = A$$

Proof:

$$A (A + B) = A.A + A.B$$

= $A + AB$

= $A$

3.

$$A + \overline{A}B = A + B$$

Proof:

$$A + \overline{A} B = A + A B + \overline{A} B$$

=  $A + (A + \overline{A}) B$

=  $A + B$

4. A.

$$(\overline{A} + B) = A$$

Proof: A.  $(\overline{A} + B) = A$ .  $\overline{A} + AB$

$= 0 + AB$

$= AB$

5.

$$AB + A. \overline{B} = A$$

6.  $(A + B). (A + \overline{B}) = A$

7.  $(A + B). (A + C) = A + B C$

8.  $AC + \overline{ABC} = AC + BC$

#### **DEMORGAN'S THEOREM:**

I.

$$\overline{A \cdot B} = \overline{A} + \overline{B}$$

II.  $\overline{A + B} = \overline{A} \cdot \overline{B}$

#### **DUALITY THEOREM:**

Duality theorem say that in the logic function applying the following changes in the AND, OR and NOT operation doesn't affect the output.

- 1. Swap '0' and '1' present in the expression.

- 2. Replacing AND operation by OR operation

- 3. Replacing OR operation by AND operation

Examples:

a.

$$A + 0 = A . 1 = A$$

b.  $A (B + C) = A B + A C$

After applying duality theorem in the above expression, it becomes

$$A + (BC) = (A + B).(A + C)$$

#### **ABSORPTIVE THEOREM:**

a. A.

$$(\overline{A} + B) = A.B$$

b. A +  $(\overline{A} \cdot B) = A + B$

#### TRANSPOSITION THEOREM:

a. A. B +

$$\overline{A}$$

. C = (A + C)( $\overline{A}$  + B)

b. (A + B).( $\overline{A}$  + C) = A. C +  $\overline{A}$ . B

USING THE THEOREM & LAWS, SIMPLIFY THE FOLLOWING EXPRESSION

2.

$$(A + B)(A + C)$$

=A.A+A.C+A.B+B.C - Distributive law

$$= A + A.C + A.B + B.C$$

- Idempotent AND law  $(A.A = A)$

$$=A+AB+BC$$

- Identity OR law  $(1 + C = 1)$

$$=A(1+B)+BC$$

$$=A+BC$$

3.

$$\overline{ABCD} + A\overline{BCD} + AB\overline{CD} + ABCD + A\overline{D} + D$$

$$= \overline{ABCD} + A\overline{BCD} + AB\overline{CD} + ABCD + A\overline{D} + D$$

$$= D(\overline{ABC} + A\overline{BC} + AB\overline{C} + ABC + 1) + A\overline{D}$$

$$= A + A\overline{D}$$

$$= (D + A)(D + \overline{D})$$

$$= A + D$$

4.  $A\overline{BC} + AB\overline{C} + ABC + ABC$

$$= A\overline{BC} + AB\overline{C} + ABC$$

$$= A\overline{BC} + AB\overline{C} + BC$$

$$= A\overline{BC} + AB\overline{C} + BC$$

$$= A\overline{BC} + B(A\overline{C} + C)$$

$$= A\overline{BC} + B(A + C)(\overline{C} + C)$$

$$= A\overline{BC} + AB + BC$$

$$= A(\overline{BC} + B) + BC$$

$$= A(B + C)(\overline{B} + B) + BC$$

$$= A(B + C) + BC$$

# Karnaugh Map For 2,3,4 Variable, Simplification Of SOPAnd POS Logic Expression Using K-Map.

#### A. BOOLEAN FUNCTION:

=AB+AC+BC

Boolean function consists of a set of Boolean variables to represent a number using Boolean connectivity's logical NOT, logical AND, logical OR operations, parenthesis and equality sign. It is also known as Boolean expression.

Based on the arrangement of literals and terms Boolean expression is classified in two types such as,

- 1. Sum of Product (SOP) form

- 2. Product of Sum (POS) form

### 1. Sum of Product (SOP) form:

Sum of Product term is consisting of sum (OR operation) of many terms; the terms may consists of single literal or product of many literals (Variables). The sum of the terms is called SOP function.

#### Example:

- i.  $F(A,B,C)=ABC+AC+AB+A\overline{B}C$

- ii.  $F(x,y,z)=xy+\overline{x}z+x\overline{y}z$

- iii.  $F(A,B,C,D) = \overline{A}B\overline{C}D + \overline{A}BCD + A\overline{B}C\overline{D} + A\overline{B}CD + ABCD$

#### a. Standard Sum of Product (SOP) form:

The SOP form of expression is said to be Standard Sum of Product form or Canonical form expression if the terms present in the expression contains all the literals present in the function.

Each individual term present in the expression must have all the literals of a function.

The steps to convert non canonical SOP to Canonical or standard SOP.

- 1. Find the missing literal in each product term.

- 2. Multiply (AND) each product term to the term having missing literal by ORing the missing literal and its complement.

- 3. Expand the terms and rearrange the literals in the product terms.

- 4. Reduce the expression by omitting the repeated terms if any(i.e. A+A=A)

#### Example:

i) Convert the given expression  $F(A, B, C) = A + \overline{BC}$  into canonical SOP form.

In the given expression, literal B and C are missing in the 1<sup>st</sup> product term. So  $(B+\overline{B})$  and  $(C+\overline{C})$  are multiplied (AND) with the term A. Similarly, literal A is missing in the 2<sup>nd</sup> product term. So  $(A+\overline{A})$  is multiplied (AND) with the product term  $\overline{B}C$ .

Given;

$$F(A,B,C)=A + \overline{B}C$$

$$=A(B + \overline{B}) + \overline{B}C(A + \overline{A})$$

$$=AB + A\overline{B} + A\overline{B}C + \overline{A}\overline{B}C$$

$$=AB(C + \overline{C}) + A\overline{B}(C + \overline{C}) + A\overline{B}C + \overline{A}\overline{B}C$$

$$=ABC + AB\overline{C} + A\overline{B}C + A\overline{B}\overline{C} + A\overline{B}C + \overline{A}\overline{B}C$$

30

$$=ABC + AB\overline{C} + A\overline{B}C + A\overline{B}\overline{C} + \overline{A}\overline{B}C$$

### 2. Product of Sum (POS) form:

Product of Sum (POS) term is consisting of sum (AND operation) of many terms; the terms may consists of single literal or product of many literals (Variables). The product of the set of sum terms is called POS function.

Example:

i.

$$F(A,B,C)=(A + B + C)(A + C)(A + B)(A + \overline{B} + C)$$

ii.

$$F(x,y,z)=(x+y)(\overline{x}+z)(x+\overline{y}+z)$$

iii.

$$F(A,B,C,D)=(\overline{A}+B+\overline{C}+D)(\overline{A}+B+C+D)(A+\overline{B}+C+\overline{D})(A+\overline{B}+C+D)$$

#### a) Standard Product of sum(POS) form:

The POS form of expression is said to be **Product of sum** form or Canonical form expression if the terms present in the expression contains all the literals present in the function.

Each individual term present in the expression must have all the literals of a function.

The steps to convert non canonical POS to Canonical or standard POS.

- 1. Find the missing literal in each sum term.

- 2. OR each sum term to the term having missing literal by ANDing(product) the missing literal and its complement.

- 3. Expand the terms and rearrange the literals in the sum terms.

- 4. Reduce the expression by omitting the repeated terms if any(i.e.  $A \cdot A = A$ )

Let us see an example here.

### Convert the given expression F(A, B, C) = (A+B)(B+C) into canonical POS form.

In the given expression, literal C is missing in the 1<sup>st</sup> sum term. So  $(C.\overline{C})$  is added with the term (A+B). Similarly, literal A is missing in the 2<sup>nd</sup> sum term. So  $(A.\overline{A})$  is added with the term (B+C).

Given;

$$F(A,B,C)=(A+B)(B+C)$$

$$=(A+B)+(C.\overline{C})(B+C)+(A.\overline{A})$$

$$=(A+B+C)(A+B+\overline{C})(A+B+C)(\overline{A}+B+C)$$

$$= (A + B + C)(A + B + \overline{C})(\overline{A} + B + C)$$

#### 3. SIMPLIFICATION OF BOOLEAN FUNCTION:

There are 3-different basic simplification methods available for minimizing Boolean function

- 1. Boolean algebra

- 2. Karnaugh map

- 3. Quine McCluskey method

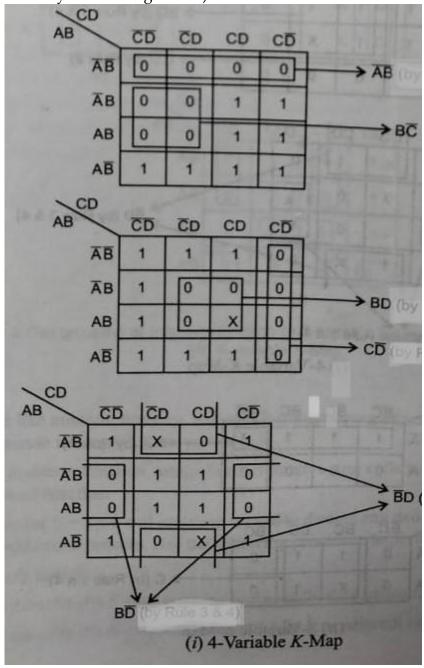

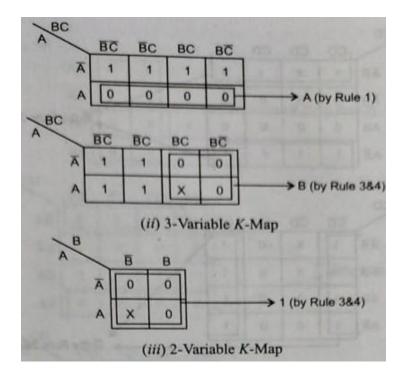

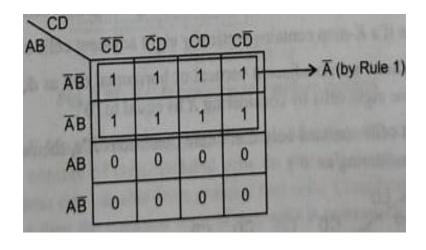

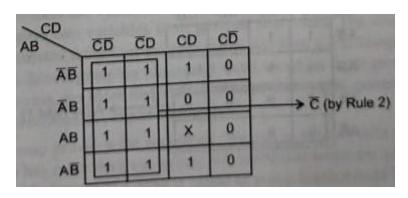

#### a. KARNAUGH MAP (K-MAP):

Simplifying the Boolean functions using Boolean postulates and theorems. It is a time consuming process and to re-write the simplified expressions after each step.

To overcome this difficulty, **Karnaugh** introduced a method for simplification of Boolean functions in an easy way.

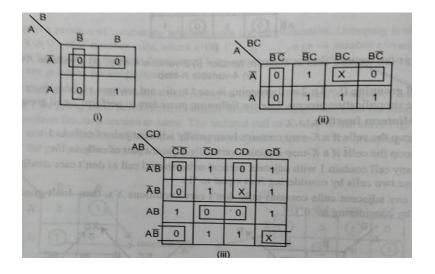

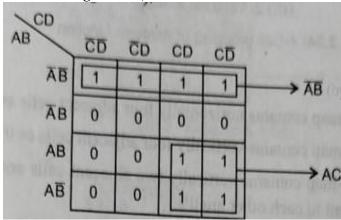

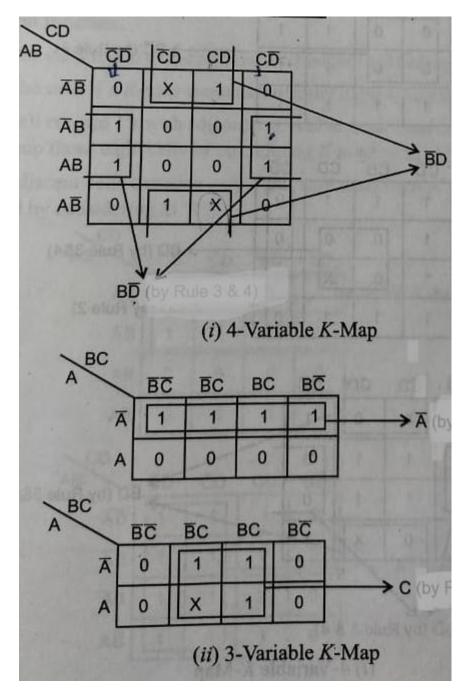

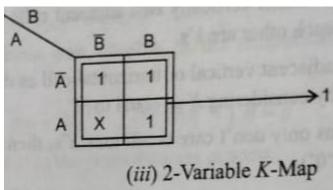

This method is a graphical method for simplification of Boolean function which consists of 2<sup>n</sup> cells for 'n' variables. Each cell of K-map represents one of the **minterm**. The adjacent cells are differed only in single bit position.

#### Classification of K-Map:

Depends on the number of variables used in the K-map it is classified as

i. 2-Variable k-map

ii. 3-Variable k-map

iii. 4- Variable k-map

iv. 5- Variable k-map

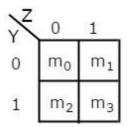

#### 1. 2- Variable k-map:

The number of variable (n) = 2

The number of cells  $=2^n=2^2=4$

The possible combinations of grouping 2 adjacent minterms are  $\{(m_0, m_1), (m_2, m_3), (m_0, m_2) \text{ and } (m_1, m_3)\}$ .

| Variable |   | Minterms                    |                |

|----------|---|-----------------------------|----------------|

| А        | В | Representation              | m <sub>i</sub> |

| 0        | 0 | $\overline{A} \overline{B}$ | $m_1$          |

| 0        | 1 | $\overline{A}B$             | $m_2$          |

| 1        | 0 | $A \overline{B}$            | $m_3$          |

| 1        | 1 | A B                         | m <sub>4</sub> |

(Minterms of 2-variable expression)

### 2. 3- Variable k-map:

The number of variable (n) = 3

The number of cells  $=2^n=2^3=8$

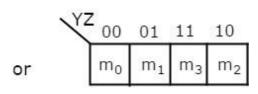

### 3. 4- Variable k-map:

The number of variable (n) = 4

The number of cells  $=2^n=2^4=16$

| WX YZ | 00              | 01              | 11              | 10              |

|-------|-----------------|-----------------|-----------------|-----------------|

| 00    | m <sub>0</sub>  | $m_1$           | m <sub>3</sub>  | m <sub>2</sub>  |

| 01    | m <sub>4</sub>  | m <sub>5</sub>  | m <sub>7</sub>  | m <sub>6</sub>  |

| 11    | m <sub>12</sub> | m <sub>13</sub> | m <sub>15</sub> | m <sub>14</sub> |

| 10    | m <sub>8</sub>  | m <sub>9</sub>  | m <sub>11</sub> | m <sub>10</sub> |

### Don't care condition:

In some digital systems, nonessential minterms or maxterms may be introduced in the input sequences. Such nonessential minterms or maxterms are called as don't care condition in the Boolean expression.

These nonessential terms never occur in the input sequence of the system.

Normally, in K-Map don't care conditions are represented by symbol 'X'. Don't care values can be taken as either '0' or '1'.

Don't care conditions occur in the digital systems under the following condition:

- i. If certain combinations of input variables are never occur, then the output functions of such combinations are considered as nonessential or don't care condition.

- ii. If certain combinations of variables are irrelevant even all the input combination of variables occurs, then the output functions of such combinations are considered as nonessential or don't care condition.

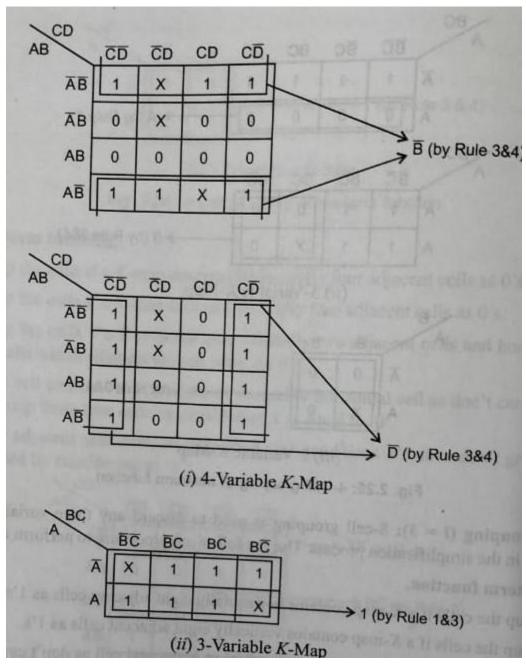

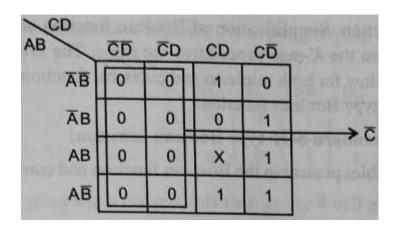

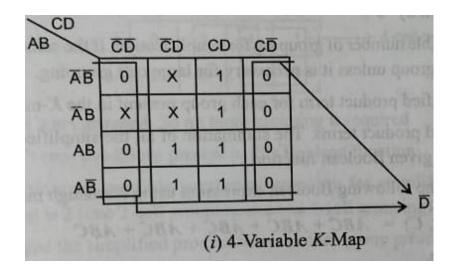

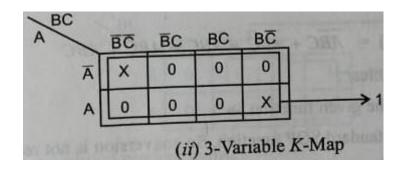

### Grouping cell for Minimization:

In K-map, minterms are marked by'1'

maxterm are marked by'0'

don't care are marked by 'd' or 'x' i.e X= '0' or '1'

In minterm function, don't care condition is considered as '1' if necessary for simplification or grouping cell. Else, it is marked by '0'

In maxterm function, don't care condition is considered as '0' if necessary for simplification or grouping cell. Else, it is marked by '1'

Grouping of cell or Loop of cell is process of combining adjacent cells for simplification.

Grouping is obtained by combining 1's or 0's of 2<sup>i</sup> number cells, where i=0,1,2...,n (n number of variables used in the Boolean function.)

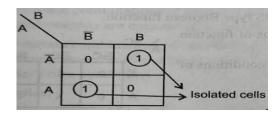

#### Isolation Cell or Single cell group(i=0):

- i. K-map cell is called as Isolation group when no adjacent horizontal or vertical cell is '1' for minterm and '0' for maxterm.

- ii. Isolation cell can't be used for simplification, it gives the Boolean function remain as same

**2- Cell group(i=1):** 2 cell grouping is used to discard any variable from two adjacent cell in the simplification process

#### **Procedure for Minterm function:**

- i. Group the cell if a k-map contains horizontally adjacent pair (2 cell) of cells as 1's

- ii. Group the cell if a k-map contains vertically adjacent pair (2 cell) of cells as 1's

- iii. If any cell contain 1 with adjacent vertical or horizontal cell as don't care condition 'X' then group those two cells by considering X=1

- iv. If any cell contain only don't care condition 'X' then don't group those cells (Discard by considering as X=0)

#### **Procedure for Maxterm function:**

- i. Group the cell if a k-map contains horizontally adjacent pair of cells as 0's

- ii. Group the cell if a k-map contains vertically adjacent pair (2 cell) of cells as 0's

- iii. If any cell contain 0 with adjacent vertical or horizontal cell as don't care condition 'X' then group those two cells by considering X=0

- iv. If any cell contain only don't care condition 'X' then don't group those cells (Discard by considering as X=1)

**4- Cell group(i=2):** 4 cell grouping is used to discard any two variables from four(4) adjacent cells in the simplification process

#### **Procedure for Minterm function:**

- i. Group the cell if a k-map contains horizontally four (4) adjacent of cells as 1's

- ii. Group the cell if a k-map contains vertically four )4) adjacent pail of cells as 1's

- iii. Group the cell If a K-map contain vertically two adjacent cell and horizontal two adjacent cell which adjacent to each other are 1's.

- iv. If any cell contain 1's with adjacent vertically or horizontal cell as don't care condition 'X' then group those four cell by considering X=1.

- v. If any adjacent cell contain only don't care condition 'X' then don't group those cells ( Discard by considering as X=0)

#### **Procedure for Maxterm function:**

- i. Group the cell if a k-map contains horizontally four (4) adjacent of cells as 0's

- ii. Group the cell if a k-map contains vertically four )4) adjacent pail of cells as 0's

- iii. Group the cell If a K-map contain vertically two adjacent cell and horizontal two adjacent cell which adjacent to each other are 0's.

- iv. If any cell contain 1's with adjacent vertically or horizontal cell as don't care condition 'X' then group those four cell by considering X=0.

- v. If any adjacent cell contain only don't care condition 'X' then don't group those cells (Discard by considering as X=1)

**8- Cell group(i=3):** 8 cell grouping is used to discard any three (3) variables from eight (8) adjacent cells in the simplification process

#### **Procedure for Minterm function:**

- i. Group the cell if a k-map contains horizontally eight (8) adjacent of cells as 1's

- ii. Group the cell if a k-map contains vertically eight (8)) adjacent pail of cells as 1's

- iii. If any cell contain 1's with adjacent vertically or horizontal cell as don't care condition 'X' then group those eight (8) cell by considering X=1.

- iv. If any adjacent cell contain only don't care condition 'X' then don't group those cells ( Discard by considering as X=0)

#### **Procedure for Maxterm function:**

- i. Group the cell if a k-map contains horizontally eight (8) adjacent of cells as 0's

- ii. Group the cell if a k-map contains vertically eight (8)) adjacent pail of cells as 0's

- iii. If any cell contain 0's with adjacent vertically or horizontal cell as don't care condition 'X' then group those eight (8) cell by considering X=0.

- iv. If any adjacent cell contain only don't care condition 'X' then don't group those cells ( Discard by considering as X=1)

| AB | CD | CD | CD | CD |       |

|----|----|----|----|----|-------|

| ĀB | 1  | 1  | 1  | 9  | 63 05 |

| ĀВ | 1  | 1  | 1  | 1  | 300   |

| АВ | 0  | 0  | 0  | 0  | -> A  |

| AB | 0  | 0  | 0  | 0  | 2 1   |

SHORT QUESTIONS AND ANSWERS

#### 1. Define digital system?

Ans. A digital system is a system which deals with discrete signal. The input and output of this system is two binary value which is 0 and 1. Examples of digital systems are mobile phones, radio, megaphones and many more

#### 2. List the applications of digital system?

**Ans.** Mobile Phones, Calculators and Digital Computers Radios and communication Devices.

#### 3. What is meant by bit?

Ans. Single digit that used to represent the number is called bit i.e 1 or 0

#### 4. What is radix number system?

Ans. Radix (base ) number system is a general representation of all the number system. It represent the weight of each digits present in the number system. Example :

Base of binary no. system =2

Base of octal no. system =8

Base of hexadecimal no. system=16

#### 5. Define binary code?

**Ans.** A group of binary bit that are used to represent the characters, numbers, letters or words or symbol is called as binary codes.

The digital data is represented, stored and transmitted as group of binary bits. This group is also called as binary code. The binary code is represented by the number as well as alphanumeric letter.

#### 6. What are weighted binary codes?

**Ans.** A code which consists of bit weight for each digit present in the binary code is called weighted binary codes

Example:

BCD codes

#### 7. What are non-weighted binary codes?

Ans. A code which is not having any bit weight for the digit present in the binary code is called non-weighted binary codes

Example: Excess-3 code, gray code.

#### 8. What is gray code? Why is it called as reflective code and cyclic code?

**Ans.** It is the non-weighted binary code, that means there are no specific weights assigned to the bit position. only one bit position will change each time the decimal number is incremented so called reflective code. Also the adjacent gray representation differs in only binary bit hence it is referred as cyclic code.

#### 9. State the associative property of Boolean algebra

**Ans.** Associative law defines that the grouping of variable in the multivariable AND and OR operation does not change the output.

i.

$$A + (B + C) = (A + B) + C$$

ii.

$$A \cdot (B \cdot C) = (A \cdot B) \cdot C$$

#### 10. State the distributive property of Boolean algebra

**Ans**. Associative law defines that the distribution of variable with AND operation over OR operation is equal to distribution of variable with OR operation over AND operation

i.

$$A + B C = (A + B) (A + C)$$

ii.

$$A (B + C) = A B + A C$$

11. State the DeMorgan's theorem

i.

$$\overline{A.B} = \overline{A} + \overline{B}$$

ii.

$$\overline{A+B}=\overline{A}.\overline{B}$$

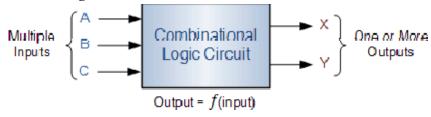

# 2.COMBINATIONAL LOGIC CIRCUITS

## Give the concept of combinational logic circuits:

A combinational circuit is the digital logic circuit in which the output depends on the combination of present inputs applied to the circuit and It does not depend past input

Combinational circuits are developed using combination of AND, OR, NOT, NAND, and NOR logic gates.

Combinational Logic Circuits are memory less digital logic circuits whose output at any instant in time depends only on the combination of its inputs

The combinational logic circuits have no feedback circuit is used.

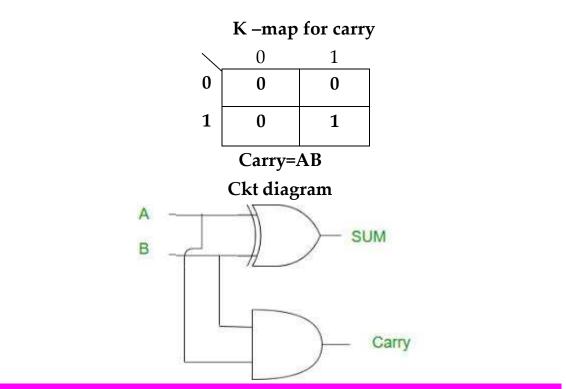

## Half adder circuit and verify its functionality using truth table:

Half adder is a combinational circuit which consists of two binary input variables called augend and addend and two binary output variables called sum and carry. In the addition result, the lower significant bit is called as sum and the higher significant bit is called as carry.

Truth table

| In | put | Output |     |  |

|----|-----|--------|-----|--|

| A  | В   | Carry  | Sum |  |

| 0  | 0   | 0      | 0   |  |

| 0  | 1   | 0      | 1   |  |

| 1  | 0   | 0      | 1   |  |

| 1  | 1   | 1      | 0   |  |

K -map for sum

$$\begin{array}{c|cccc}

& 0 & 1 \\

& 0 & 1 \\

& 1 & 0 \\

\end{array}$$

$$Sum=\overline{A}B + A\overline{B} = A \oplus B$$

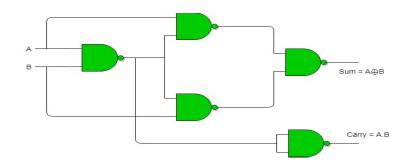

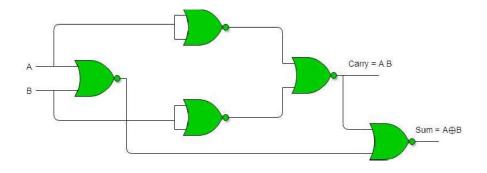

Realize a Half-adder using NAND gates only and NOR gates only.

Half-adder using NAND gates

Half-adder using NAND gates

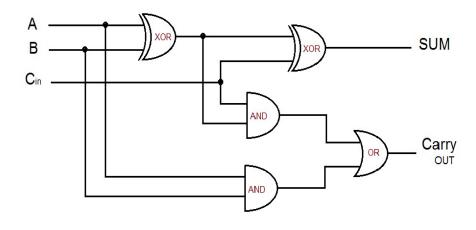

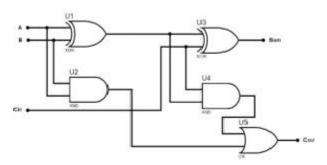

## Full adder circuit and explain its operation with truth table:

Full adder is a combinational circuit which consists of three binary input variables called augend and addend and two binary output variables called sum and carry. In the addition result, the lower significant bit is called as sum and the higher significant bit is called as carry

Truth table

Outputs Inputs В  $C_{\text{out}}$ Α  $C_{\text{in}}$

K-map can be simplified as

SUM =

$$\overline{A} \, \overline{B} \, C_{in} + \overline{A} \, B \, \overline{C}_{in} + A \, \overline{B} \, \overline{C}_{in} + A \, B \, C_{in}$$

=  $C_{in} \, (\overline{A} \, \overline{B} + A \, B) + \overline{C}_{in} \, (A \, \overline{B} + \overline{A} \, B)$

=  $C_{in} \, \left[ (\overline{A} + B) \cdot (A + \overline{B}) \right] + \overline{C}_{in} \, (A \, \overline{B} + \overline{A} \, B)$

=  $C_{in} \, (\overline{A} \, \overline{B} \cdot \overline{A} \, B) + \overline{C}_{in} \, (A \, \overline{B} + \overline{A} \, B)$

=  $C_{in} \, (\overline{A} \, \overline{B} + \overline{A} \, B) + \overline{C}_{in} \, (A \, \overline{B} + \overline{A} \, B)$

=  $C_{in} \, (\Phi(A \, \overline{B} + \overline{A} \, B)$

=  $C_{in} \, (A \, \overline{B} + \overline{A} \, B)$

Full adder circuit diagram

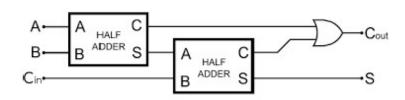

# Realize full-adder using two Half-adders and an OR – gate and write truth table.

The full adder can be implemented with two half adders by cascading them. The sum output of first half adder is Ex-OR of A and B. The sum output of full adder is Ex-OR of Cin and output of first half adder.

Truth table

|   | Inputs | Οι  | ıtputs |   |

|---|--------|-----|--------|---|

| A | В      | Cin | Cout   | S |

| 0 | 0      | 0   | 0      | 0 |

| 0 | 0      | 1   | 0      | 1 |

| 0 | 1      | 0   | 0      | 1 |

| 0 | 1      | 1   | 1      | 0 |

| 1 | 0      | 0   | 0      | 1 |

| 1 | 0      | 1   | 1      | 0 |

| 1 | 1      | 0   | 1      | 0 |

| 1 | 1      | 1   | 1      | 1 |

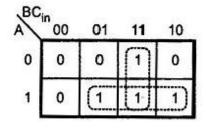

#### k-map

# For Carry (Cout)

#### For Sum

K-map can be simplified as

$$\begin{aligned} \textbf{SUM} &= \overline{A}\,\overline{B}\,C_{in} + \overline{A}\,B\,\overline{C}_{in} + A\,\overline{B}\,\overline{C}_{in} + A\,B\,C_{in} \\ &= C_{in}\,\left(\overline{A}\,\overline{B} + A\,B\right) + \overline{C}_{in}\,\left(A\,\overline{B} + \overline{A}\,B\right) \\ &= C_{in}\,\left[\left(\overline{A} + \underline{B}\right)\cdot\left(A + \overline{B}\right)\right] + \overline{C}_{in}\,\left(A\,\overline{B} + \overline{A}\,B\right) \\ &= C_{in}\,\left(\overline{A}\,\overline{B}\cdot\overline{A}\,B\right) + \overline{C}_{in}\,\left(A\,\overline{B} + \overline{A}\,B\right) \\ &= C_{in}\,\left(\overline{A}\,\overline{B} + \overline{A}\,B\right) + \overline{C}_{in}\,\left(A\,\overline{B} + \overline{A}\,B\right) \\ &= C_{in}\,\left(\overline{A}\,\overline{B} + \overline{A}\,B\right) \\ &= C_{in}\,\left(\overline{A}\,\overline{B} + \overline{A}\,B\right) \\ &= C_{in}\,\left(\overline{A}\,\overline{B} + \overline{A}\,B\right) \end{aligned}$$

Cout =

$$BC_{in} + AC_{in} + AB$$

=  $(A + \overline{A})BC_{in} + (B + \overline{B})AC_{in} + AB$

=  $ABC_{in} + \overline{A}BC_{in} + BAC_{in} + \overline{B}AC_{in} + AB$

=  $\overline{A}BC_{in} + \overline{B}AC_{in} + ABC_{in} + AB$

=  $C_{in}(\overline{A}B + \overline{B}A) + ABC_{in} + AB$

=  $C_{in}(A \oplus B) + AB(C_{in} + 1)$

=  $C_{in}(A \oplus B) + AB$

Block diagram

Circuit diagram

Full subtractor circuit and explain its operation with truth table.:

# a. Half adder circuit and verify its functionality using truth table:

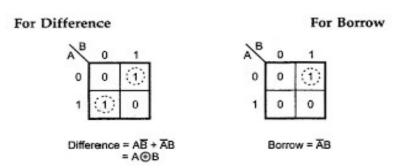

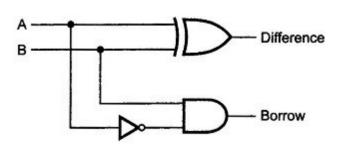

Half subtract is a combinational circuit which consists of two binary input variables called minuend and subtrahend and two binary output variables called difference and borrow. In the two bit result, the lower significant bit is called as difference and the higher significant bit is called as borrow.

Truth table

| Α | В | Borrow | Difference |

|---|---|--------|------------|

| 0 | 0 | 0      | 0          |

| 0 | 1 | 1      | 1          |

| 1 | 0 | 0      | 1          |

| 1 | 1 | 0      | 0          |

# K- map

# Logic diagram

## b.Full subtractor circuit nd explain its operation with truth table.:

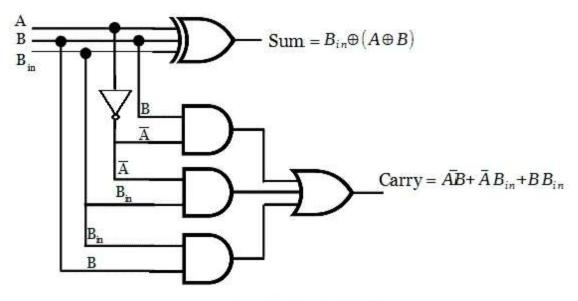

Full subtraction is a combinational circuit which consists of three binary input variables called minuends and subtrahends and two binary output variables called difference and borrow out. In the subraction result, the lower significant bit is called as difference and the higher significant bit is called as borrow out

Truth table

|   | Inputs | Out | puts |      |

|---|--------|-----|------|------|

| A | В      | Bin | D    | Bout |

| 0 | 0      | 0   | 0    | 0    |

| 0 | 0      | 1   | _1   | 1    |

| 0 | 1      | 0   | 1    | 1    |

| 0 | 1      | 1   | 0    | -1   |

| 1 | 0      | 0   | 1    | 0    |

| 1 | 0      | 1   | 0    | 0    |

| 1 | 1      | 0   | 0    | 0    |

| 1 | 1      | 1.  | -1   | - 1  |

Table 3.9 Truth table for full-subtractor

#### K-map Simplification of Difference (D) and Borrow (B)

For D

$$D = \overline{A} \overline{B} B_{in} + \overline{A} B \overline{B}_{in} + A \overline{B} \overline{B}_{in} + ABB_{in}$$

For Bout

Difference =

$$\overline{A} \, \overline{B} B_{in} + \overline{A} \, B \, \overline{B}_{in} + A \, \overline{B} \, \overline{B}_{in} + A \, B B_{in}$$

=  $B_{in} (\overline{A} \, \overline{B} + A \, B) + \overline{B}_{in} (\overline{A} \, B + A \, \overline{B})$

=  $B_{in} (A \odot B) + \overline{B}_{in} (A \oplus B)$

=  $B_{in} (\overline{A} \oplus \overline{B}) + \overline{B}_{in} (A \oplus B)$

=  $B_{in} \oplus (A \oplus B)$

Logic circuit for Full subtractor

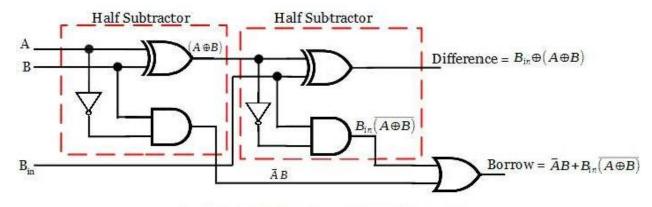

# 2.5 Realize full-subtraction using two Half-subtractor and an OR – gate and write truth table.

The full subtractor can be implemented with two half subtractors by cascading them. The difference output of first half subtractor is Ex-OR of A and B. The difference output of full subtractor is Ex-OR of Bin and output of first half subtractor.

Similarly, the borrow output of first half subtractor is ORed with the borrow output of second half subtractor to get the borrow output of full subtractor.

## Simplification of Difference and Borrow

Difference =

$$\overline{A} \, \overline{B} B_{in} + \overline{A} \, B \, \overline{B}_{in} + A \, \overline{B} \, \overline{B}_{in} + A \, B \, B_{in}$$

=  $B_{in} (\overline{A} \, \overline{B} + A \, B) + \overline{B}_{in} (\overline{A} \, B + A \, \overline{B})$

=  $B_{in} (A \odot B) + \overline{B}_{in} (A \oplus B)$

=  $B_{in} (\overline{A} \oplus \overline{B}) + \overline{B}_{in} (A \oplus B)$

=  $B_{in} \oplus (A \oplus B)$

Borrow =

$$\overline{A} B + \overline{A} B_{in} + B B_{in}$$

=  $\overline{A} B + \overline{A} B_{in} (B + \overline{B}) + B B_{in} (A + \overline{A})$

=  $\overline{A} B + \overline{A} B B_{in} + \overline{A} \overline{B} B_{in} + A B B_{in} + \overline{A} B B_{in}$

=  $\overline{A} B (1 + B_{in} + B_{in}) + \overline{A} \overline{B} B_{in} + A B B_{in}$

=  $\overline{A} B + \overline{A} \overline{B} B_{in} + A B B_{in}$

=  $\overline{A} B + B_{in} (\overline{A} \overline{B} + A B)$

=  $\overline{A} B + B_{in} (A \odot B)$

=  $\overline{A} B + B_{in} (\overline{A} \odot B)$

Using the simplified boolean expressions for difference and l orrow output, the full subtractor can be realized

Realization of full subtractor with two half subtractors

# 2.7 Operation of 4 X 1 Multiplexers and 1 X 4 demultiplexer

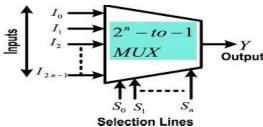

**Multiplexer** is a combinational circuit that has maximum of 2<sup>n</sup> number data inputs, 'n' number of selection control lines and single output line. O e of these data inputs will be connected to the output based on the values of selection lines. Shown in figure.

Where  $I_0$ ,  $I_1$ ,  $I_3$ ,  $I_4$ ...... $I_n$  are the input line, Y is the out put line and  $S_0$ ,  $S_1$ ,.... $S_n$  are the selection line.

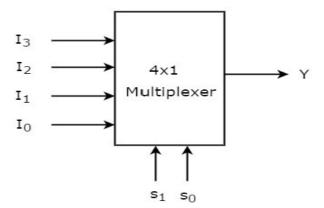

### a. 4x1 Multiplexer

4x1 Multiplexer has four data inputs I<sub>3</sub>, I<sub>2</sub>, I<sub>1</sub> & I<sub>0</sub>, two selection lines s<sub>1</sub> & s<sub>0</sub> and one output Y. The **block diagram** of 4x1 Multiplexer is shown in the following figure.

One of these 4 inputs will be connected to the output based on the combination of inputs present at these two selection lines. Truth table of 4x1 Multiplexer is shown below.

| Selection      | Selection Lines |                |  |

|----------------|-----------------|----------------|--|

| S <sub>1</sub> | S <sub>0</sub>  | Y              |  |

| 0              | 0               | I <sub>0</sub> |  |

| 0              | 1               | I <sub>1</sub> |  |

| 1              | 0               | l <sub>2</sub> |  |

| 1              | 1               | l <sub>3</sub> |  |

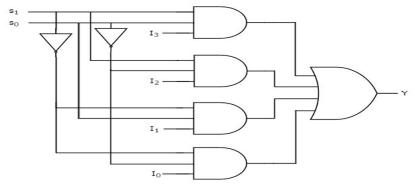

$$Y = \overline{S_1} \, \overline{S_0} \, I_0 + \overline{S_1} \, S_0 \, I_1 + S_1 \, \overline{S_0} \, I_2 + S_1 \, S_0 I_3$$

Logic circuit diagram

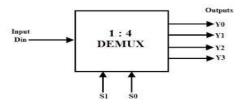

## De-Multiplexer:

**De-Multiplexer** is a combinational circuit that performs the reverse operation of Multiplexer. It has single input, 'n' selection lines and maximum of 2<sup>n</sup> outputs. De-Multiplexer is also called as **De-Mux**.

## 1x4 De-Multiplexer

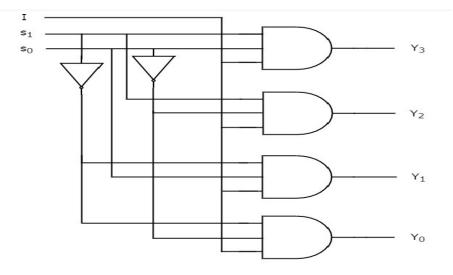

1x4 De-Multiplexer has one input I, two selection lines, s1 & s0 and four outputs Y3, Y2, Y1 &Y0. The block diagram of 1x4 De-Multiplexer is shown in the following figure.

The single input 'I' will be connected to one of the four outputs, Y3 to Y0 based on the values of selection lines s1 & s0. The Truth table of 1x4 De-Multiplexer is shown below.

|                | Selection inputs |            | outputs        |                       |                |

|----------------|------------------|------------|----------------|-----------------------|----------------|

| S <sub>1</sub> | S <sub>0</sub>   | <b>Y</b> 3 | Y <sub>2</sub> | <b>Y</b> <sub>1</sub> | Y <sub>0</sub> |

| 0              | 0                | 0          | 0              | 0                     | 1              |

| 0              | 1                | 0          | 0              | 1                     | 0              |

| 1              | 0                | 0          | 1              | 0                     | 0              |

| 1              | 1                | 1          | 0              | 0                     | 0              |

From the above Truth table, we can directly write the **Boolean functions** for each output as

$$Y_0=I \overline{S_1} \overline{S_0}$$

$$Y_1=I \overline{S_1} S_0$$

$$Y_2=I S_1 \overline{S_0}$$

$$Y_3=I S_1 S_0$$

Logic circuit diagram

### Working of Binary-Decimal Encoder & 3 X 8 Decoder.

#### a. **Decoder**

Decoder is a combinational circuit that has multiple input multiple output that is 'n' number of input lines and maximum of 2<sup>n</sup> number of output lines.

One of these outputs will be active High based on the combination of inputs present, when the decoder is enabled. That means decoder detects a particular code. i.e In the decoder, the combination of input information lines define the log c output of any one.

output line as logic high at a time and the rest of the output lines are being fixed to logic 0. The outputs of the decoder are nothing but the min terms of 'n' input variables lines, when it is enabled.

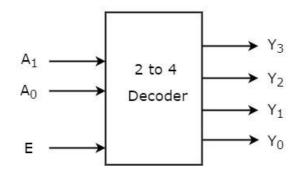

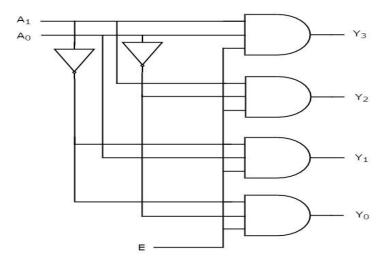

# 2 to 4 Decoder

Let 2 to 4 Decoder has two inputs  $A_1$  &  $A_0$  and four outputs  $Y_3$ ,  $Y_2$ ,  $Y_1$  &  $Y_0$ . The **block** diagram of 2 to 4 decoder is shown in the following figure.

i.e input lines 'n'=2

output lines=2<sup>n</sup>=2<sup>2</sup>=4

One of these four outputs will be '1' for each combination of inputs when enable, E is '1'. The **Truth table** of 2 to 4 decoder is shown below.

| Enable | Inputs         |                | Outputs               |                |                |                |

|--------|----------------|----------------|-----------------------|----------------|----------------|----------------|

| Е      | A <sub>1</sub> | A <sub>0</sub> | <b>Y</b> <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Y <sub>0</sub> |

| 0      | Х              | Х              | 0                     | 0              | 0              | 0              |

| 1      | 0              | 0              | 0                     | 0              | 0              | 1              |

| 1      | 0              | 1              | 0                     | 0              | 1              | 0              |

| 1      | 1              | 0              | 0                     | 1              | 0              | 0              |

| 1      | 1              | 1              | 1                     | 0              | 0              | 0              |

From Truth table, we can write the **Boolean functions** for each output as

$$Y_0 = E \overline{A_1} \overline{A_0}$$

$$Y_1 = E \overline{A_1} A_0$$

$$Y_2 = E A_1 \overline{A}_0$$

$$Y_3 = E A_1 A_0$$

## 3 to 8 Decoder

Let 3 to 8 Decoder has 3 inputs  $A_2$   $A_1$  &  $A_0$  and 8 outputs  $Y_7$ ,  $Y_6$ ,  $Y_5$ ,  $Y_4$ ,  $Y_3$ ,  $Y_2$ ,  $Y_1$  &  $Y_0$ . The **block diagram** of 3 to 8 decoder is shown in the following figure.

i.e input lines 'n'=3

output lines=2<sup>n</sup>=2<sup>3</sup>=8

| Enable | I          | nput       | s              | Outputs        |                |    |                |            |                |    |                       |

|--------|------------|------------|----------------|----------------|----------------|----|----------------|------------|----------------|----|-----------------------|

| Е      | <b>A</b> 3 | <b>A</b> 1 | A <sub>0</sub> | Y <sub>7</sub> | Y <sub>6</sub> | Y5 | Y <sub>4</sub> | <b>Y</b> 3 | Y <sub>2</sub> | Y1 | <b>Y</b> <sub>0</sub> |

| 0      | X          | Х          | Х              | 0              | 0              | 0  | 0              | 0          | 0              | 0  | 0                     |

| 1      | 0          | 0          | 0              | 0              | 0              | 0  | 0              | 0          | 0              | 0  | 1                     |

| 1      | 0          | 0          | 1              | 0              | 0              | 0  | 0              | 0          | 0              | 1  | 0                     |

| 1      | 0          | 1          | 0              | 0              | 0              | 0  | 0              | 0          | 1              | 0  | 0                     |

| 1      | 0          | 1          | 1              | 0              | 0              | 0  | 0              | 1          | 0              | 0  | 0                     |

| 1      | 1          | 0          | 0              | 0              | 0              | 0  | 1              | 0          | 0              | 0  | 0                     |

| 1      | 1          | 0          | 1              | 0              | 0              | 1  | 0              | 0          | 0              | 0  | 0                     |

| 1      | 1          | 1          | 0              | 0              | 1              | 0  | 0              | 0          | 0              | 0  | 0                     |

| 1      | 1          | 1          | 1              | 1              | 0              | 0  | 0              | 0          | 0              | 0  | 0                     |

From Truth table, we can write the **Boolean functions** for each output as

$$Y_0 = E \overline{A}_2 \overline{A}_1 \overline{A}_0$$

$$Y_1 = E \overline{A}_2 \overline{A}_1 A_0$$

$$Y_2 = E \overline{A}_2 A_1 \overline{A}_0$$

$$Y_3 = E \overline{A}_2 A_1 \overline{A}_0$$

$$Y_4 = E A_2 \overline{A}_1 \overline{A}_0$$

$$Y_5 = E A_2 \overline{A}_1 A_0$$

$$Y_6 = E A_2 \overline{A}_1 \overline{A}_0$$

$$Y_7 = E A_2 A_1 \overline{A}_0$$

Logical circuit of the above expressions is given below:

Logic diagram 3 to 8 line decoder

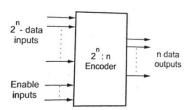

### **Encoder:**

An encoder is a multiple input multi output combinational digital circuit that performs the inverse operation of a decoder. It means that an encoder converts the 2<sup>n</sup> number of coded inputs into n number of coded outputs.

The output lines of a digital encoder generate the binary equivalent of the input line whose value is equal to 1 and are available to encode either a decimal or hexadecimal input pattern to typically a binary or B.C.D (binary coded decimal) output code

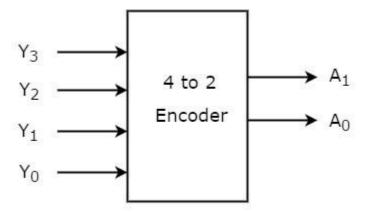

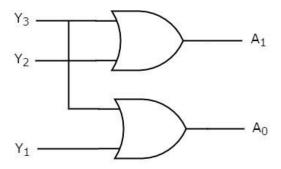

#### 4 to 2 line Encoder:

There are four inputs (Y0, Y1, Y2, and Y3) and two outputs (A0 and A1) in the 4 to 2 line encoder. In addition, To get the respective binary code on the output side, one

input line at a time is set to true in a 4-input line. The 4 to 2 line encoder's block diagram and truth table are shown below.

|            | Inp            | Out                   | puts  |                |       |

|------------|----------------|-----------------------|-------|----------------|-------|

| <b>Y</b> 3 | Y <sub>2</sub> | <b>Y</b> <sub>1</sub> | $Y_0$ | A <sub>1</sub> | $A_0$ |

| 0          | 0              | 0                     | 1     | 0              | 0     |

| 0          | 0              | 1                     | 0     | 0              | 1     |

| 0          | 1              | 0                     | 0     | 1              | 0     |

| 1          | 0              | 0                     | 0     | 1              | 1     |

The terms A<sub>0</sub> and A<sub>1</sub> are logically expressed as follows:

$$A_1 = Y_3 + Y_2$$

$A_0 = Y_3 + Y_1$

# Circuit Diagram

Two input OR gates can be used to implement the aforementioned two Boolean functions. Further, The 4 to 2 encoder circuit diagram is given in the graphic below.

#### **Uses of Encoder**

In all digital systems, these systems are relatively simple to operate.

To convert a decimal number to a binary number, encoders are employed. The goal is to complete a binary operation like addition, subtraction, multiplication, and so on.

## Disadvantages

The disadvantages of a standard encoder are listed below.

- When all of the encoder's outputs are 0, there is ambiguity. Because when only the least significant input is one or when all inputs are zero, it could be the code  $\pi$  atching the inputs.

- When more than one input is set to high, the encoder generates an output that may or may not be the proper code. If both Y3 and Y6 are '1', for example, the encoder outputs 111. This is neither the comparable code for Y3, when it is '1', nor is it the equivalent code for Y6, when it is '1'.

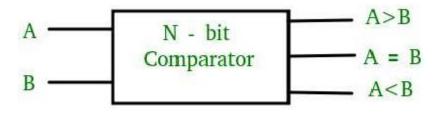

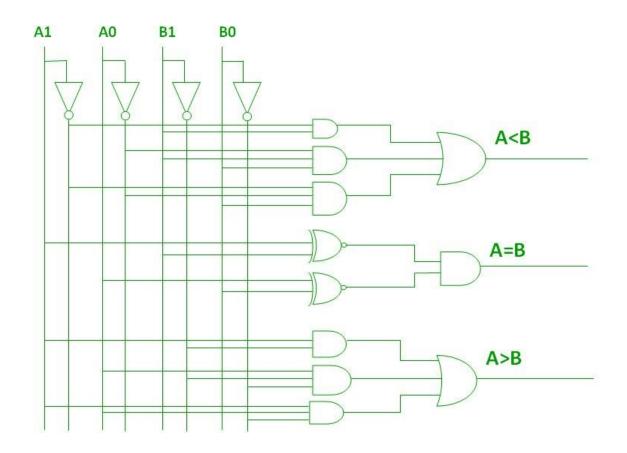

# Working of Two bit magnitude comparator.

A magnitude digital Comparator is a combinational circuit that **compares two digital or binary numbers** in order to find out whether one binary number is equal, less than, or greater than the other binary number. We logically design a circuit for which we will have two inputs one for A and the other for B and have three output terminals, one for A > B condition, one for A = B condition, and one for A < B condition.

Truth table

|            | Inj   | out            |                | Out put |     |                   |

|------------|-------|----------------|----------------|---------|-----|-------------------|

| F          | A     | I              | В              | A>B     | A=B | A <b< td=""></b<> |

| <b>A</b> 1 | $A_0$ | $\mathbf{B}_1$ | $\mathbf{B}_0$ |         |     |                   |

| 0          | 0     | 0              | 0              | 0       | 1   | 0                 |

| 0          | 0     | 0              | 1              | 0       | 0   | 1                 |

| 0          | 0     | 1              | 0              | 0       | 0   | 1                 |

| 0          | 0     | 1              | 1              | 0       | 0   | 1                 |

| 0          | 1     | 0              | 0              | 1       | 0   | 0                 |

| 0          | 1     | 0              | 1              | 0       | 1   | 0                 |

| 0          | 1     | 1              | 0              | 0       | 0   | 1                 |

| 0 | 1 | 1 | 1 | 0 | 0 | 1 |

|---|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 1 | 0 |

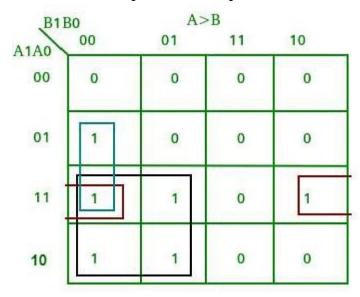

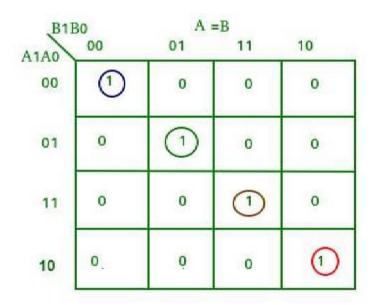

From the above truth table K-map for each output can be drawn as follows:

$A>B=A_1A_0\bar{B}_0+\bar{B}_1\bar{B}_0A_0+A_1\bar{B}_1$

$A=B = \bar{A}_1 \bar{A}_0 \bar{B}_1 \bar{B}_0 + \bar{A}_1 A_0 \bar{B}_1 B_0 + A_1 A_0 B_1 B_0 + A_1 \bar{A}_0 B_1 \bar{B}_0$

$$= (A \ \overline{B_1}(\bar{A}_0\bar{B}_0 + A_0B_0) + A_1B_1(A_0B_0 + \bar{A}_0\bar{B}_0)$$

$$= (A \ \overline{B_1} + A_1B_1)(A_0B_0 + \bar{A}_0\bar{B}_0)$$

$$= (A_1 \odot B_1)(A_0 \odot B_0)$$

| B1B0 |    | A  |    |    |

|------|----|----|----|----|

| A1A0 | 00 | 01 | 11 | 10 |

| 00   | 0  | 1  | 1  | 1  |

| 01   | 0  | 0  | 1  | 1  |

| 11   | 0  | 0  | 0  | 0  |

| 10   | 0  | 0  | 1  | 0  |

| 28   | o. |    |    |    |

$A < B = A_1 A_0 B_1 + B_1 B_0 A_0 + A_1 B_1$

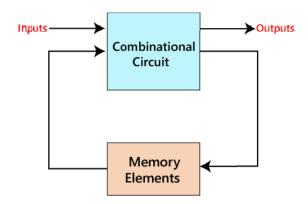

# **3.SEQUENTIAL LOGIC CIRCUITS**

The outputs of the sequential circuits depend on both the combination of present inputs and previous outputs. The previous output is treated as the present state. So, the sequential circuit contains the combinational circuit and its memory storage elements. A sequential circuit doesn't need to always contain a combinational circuit. So, the sequential circuit can contain only the memory element.

BLOCK DIAGRAM OF SEQUENTIAL CKT

Difference between the combinational circuits and sequential circuits are given below:

|   | <b>Combinational Circuits</b>           | Sequential Circuits                         |  |  |

|---|-----------------------------------------|---------------------------------------------|--|--|

| 1 | The outputs of the combinational        | The outputs of the sequential circuits      |  |  |

|   | circuit depend only on the present      | depend on both present inputs and           |  |  |

|   | inputs                                  | present state(previous output).             |  |  |

| 2 | The feedback path is not present in the | The feedback path is present in the         |  |  |

|   | combinational circuit.                  | sequential circuits.                        |  |  |

| 3 | In combinational circuits, memory       | In the sequential circuit, memory           |  |  |

|   | elements are not required.              | elements play an important role and         |  |  |

|   |                                         | require.                                    |  |  |

| 4 | The clock signal is not required for    | The clock signal is required for sequential |  |  |

|   | combinational circuits.                 | circuits.                                   |  |  |

| 5 | The combinational circuit is simple to  | It is not simple to design a sequential     |  |  |

|   | design.                                 | circuit.                                    |  |  |

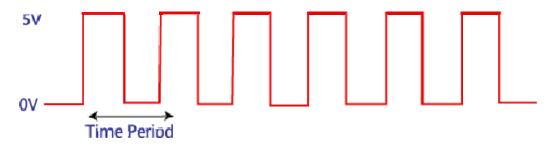

State the necessity of clock and give the concept of level clocking and edge triggering,

#### 1. Clock:

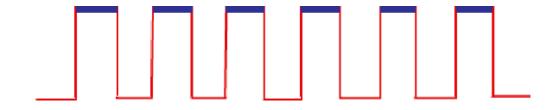

A clock signal is a periodic signal in which ON time and OFF time need not be the same. When ON time and OFF time of the clock signal are the same, a square wave is used to represent the clock signal. Below is a diagram which represents the clock signal:

A clock signal is considered as the square wave. Sometimes, the signal stays at logic, either high 5V or low 0V, to an equal amount of time. It repeats with a certain time period, which will be equal to twice the 'ON time' or 'OFF time'.

## Types of Triggering

These are two types of triggering in sequential circuits:

## Level triggering

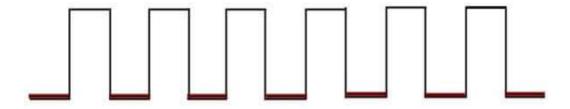

The logic High and logic  $Lo_V$  are the two levels in the clock signal. In level triggering, when the clock pulse is at a particular level, only then the circuit is actia ted. There are the following types of level triggering:

# Positive level triggering

In a positive level triggering, the signal with Logic High occurs. So, in this triggering, the circuit is operated with such type of clock signal. Below is the diagram of positive level triggering:

#### Negative level triggering

In negative level triggering, the signal with Logic Low occurs. So, in this triggering, the circuit is operated with such type of clock signal. Below is the diagram of Negative level triggering:

#### Edge triggering

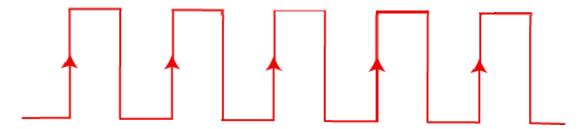

In clock signal of edge triggering, two types of transitions occur, i.e., transition either from Logic Low to Logic High or Logic High to Logic Low.

Based on the transitions of the clock signal, there are the following types of edge triggering:

#### Positive edge triggering

The transition from Logic Low to Logic High occurs in the clock signal of positive edge triggering. So, in positive edge triggering, the circuit is operated with such type of clock signal. The diagram of positive edge triggering is given below.

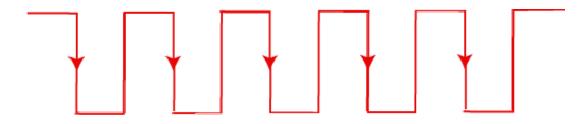

# Negative edge triggering

The transition from Logic High to Logic low occurs in the clock signal of negative edge triggering. So, in negative edge triggering, the circuit is operated with such type of clock signal. The diagram of negative edge triggering is given below.

### What is flip flop?

Flip-Flop is popularly known as the basic digital memory circuit. It is an edge triggered synchronous sequential logic circuit that is capable of storing single bit binary information. It has two states as logic 1(High) and logic 0(low) states. A flip flop is a sequential circuit which consists of a single binary state of information or data. The digital circuit is a flip flop which has two outputs and are of opposite states. It is also known as a Bistable Multivibrator.

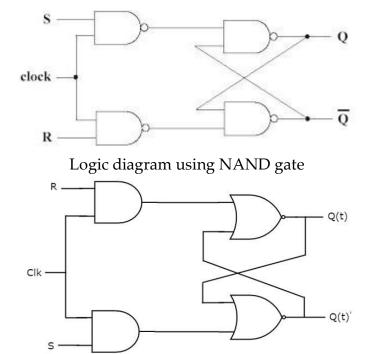

#### **Clocked SR flip flop**

SR (Set-Reset) flip-flop is a clocked sequential circuit which is controlled by edge triggered CLK control signal.

Logic diagram using AND and NOR gate

Truth Table

| Inputs |   |   | Out | tputs   | States     |

|--------|---|---|-----|---------|------------|

| CLK    | S | R | Q   | $ar{Q}$ |            |

| 0      | 0 | 0 | NC  | NC      | No. change |

| 0      | 0 | 1 | NC  | NC      | No. change |

| 0      | 1 | 0 | NC  | NC      | No. change |

| 0      | 1 | 1 | NC  | NC      | No. change |

| 1      | 0 | 0 | NC  | NC      | No. change |

| 1      | 0 | 1 | 0   | 1       | Reset      |

| 1      | 1 | 0 | 1   | 0       | Set        |

| 1      | 1 | 1 | X   | X       | No. change |

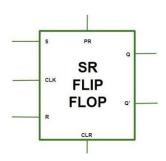

#### 3.3 Clocked SR flip flop with preset and clear inputs.

In SR flip flop, with the help of Preset and Clear, when the power is switched ON, the state of the circuit keeps on changing, i.e. it is uncertain. It may come to Set (Q = 1) or Reset (Q' = 0) state. In many applications, it is desired to initially Set or Reset the flip flop. This thing is accomplished by the Preset (PR) and the Clear (CLR).

**BLOCK DIAGRAM OF F/F**

#### Operations in SR Flip-Flop -

#### • Case-1:

PR = CLR = 1

The asynchronous inputs are inactive and the flip flop responds freely to the S, R and the CLK inputs in the normal way.

#### • Case-2:

PR = 0 and CLR = 1

This is used when the Q is set to 1.

#### Case-3:

PR = 1 and CLR = 0

This is used when the Q' is set to 1.

#### Case-4:

PR = CLR = 0

This is an invalid state.

| INPUTS |     |     |    |    | OUTPUTS |                   | Comments   |

|--------|-----|-----|----|----|---------|-------------------|------------|

| PR     | CLR | CLK | S  | R  | Q(n+1)  | $ar{Q}_{(n+1)}$   |            |

| 0      | 1   | NA  | NA | NA | 1       | 0                 | Set        |

| 1      | 0   | NA  | NA | NA | 0       | 1                 | Re-set     |

| 1      | 1   | 0   | NA | NA | Qn      | $ar{Q}_{	ext{n}}$ | No. change |

| 1 | 1 | 1 | 0 | 0 | Qn | $ar{Q}_{\mathrm{n}}$ | No. change  |

|---|---|---|---|---|----|----------------------|-------------|

| 1 | 1 | 1 | 1 | 0 | 1  | 0                    | Set         |

| 1 | 1 | 1 | 0 | 1 | 0  | 1                    | Re-set      |

| 1 | 1 | 1 | 1 | 1 | Х  | Х                    | Not allowed |

#### **Applications of Flip-Flop:**

- 1. Flip flops are used as a bounce elimination switch.

- 2. They are used as a serial to parallel and parallel to serial conversion.

- 3. It is used for counters.

- 4. It is used for frequency divider and also as a latch.

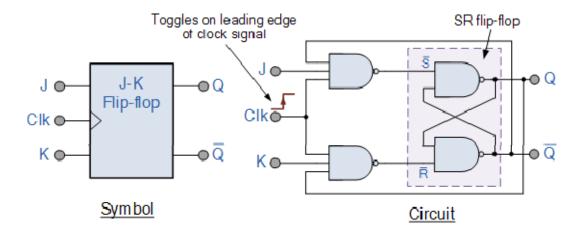

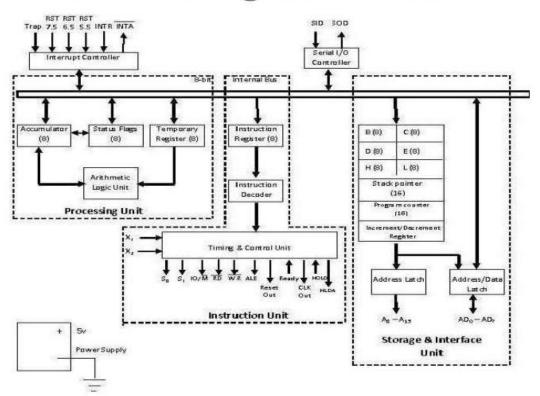

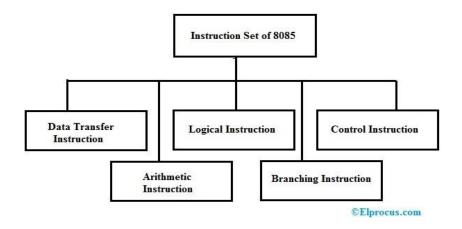

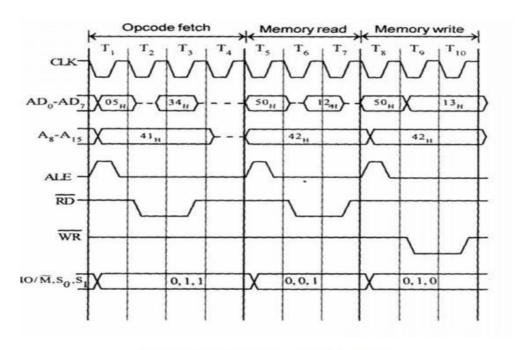

# 3.5 Construct level clocked JK flip flop using S-R flip-flop and explain with truth table